后摩爾時(shí)代的創(chuàng)新:在米爾FPGA上實(shí)現(xiàn)Tiny YOLO V4,助力AIoT應(yīng)用

http://www.sharifulalam.com 2024-11-21 13:32 來源:米爾電子

Tip:學(xué)習(xí)如何在 MYIR 的 ZU3EG FPGA 開發(fā)板上部署 Tiny YOLO v4,對(duì)比 FPGA、GPU、CPU 的性能,助力 AIoT 邊緣計(jì)算應(yīng)用。(文末有彩蛋)

一、 為什么選擇 FPGA:應(yīng)對(duì) 7nm 制程與 AI 限制

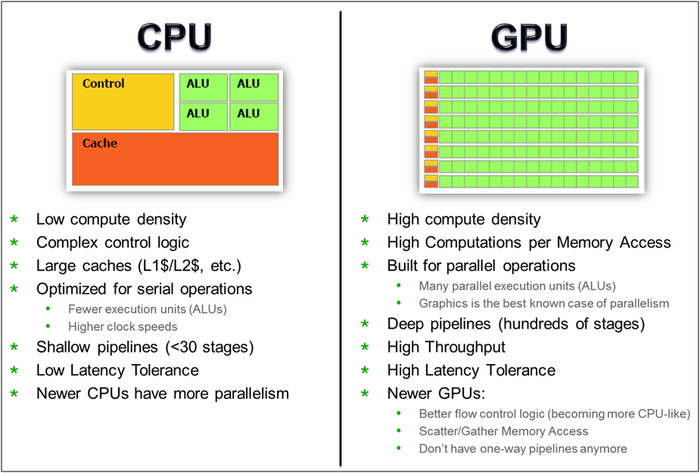

在全球半導(dǎo)體制程限制和高端 GPU 受限的大環(huán)境下,F(xiàn)PGA 成為了中國(guó)企業(yè)發(fā)展的重要路徑之一。它可支持靈活的 AIoT 應(yīng)用,其靈活性與可編程性使其可以在國(guó)內(nèi)成熟的 28nm 工藝甚至更低節(jié)點(diǎn)的制程下實(shí)現(xiàn)高效的硬件加速。

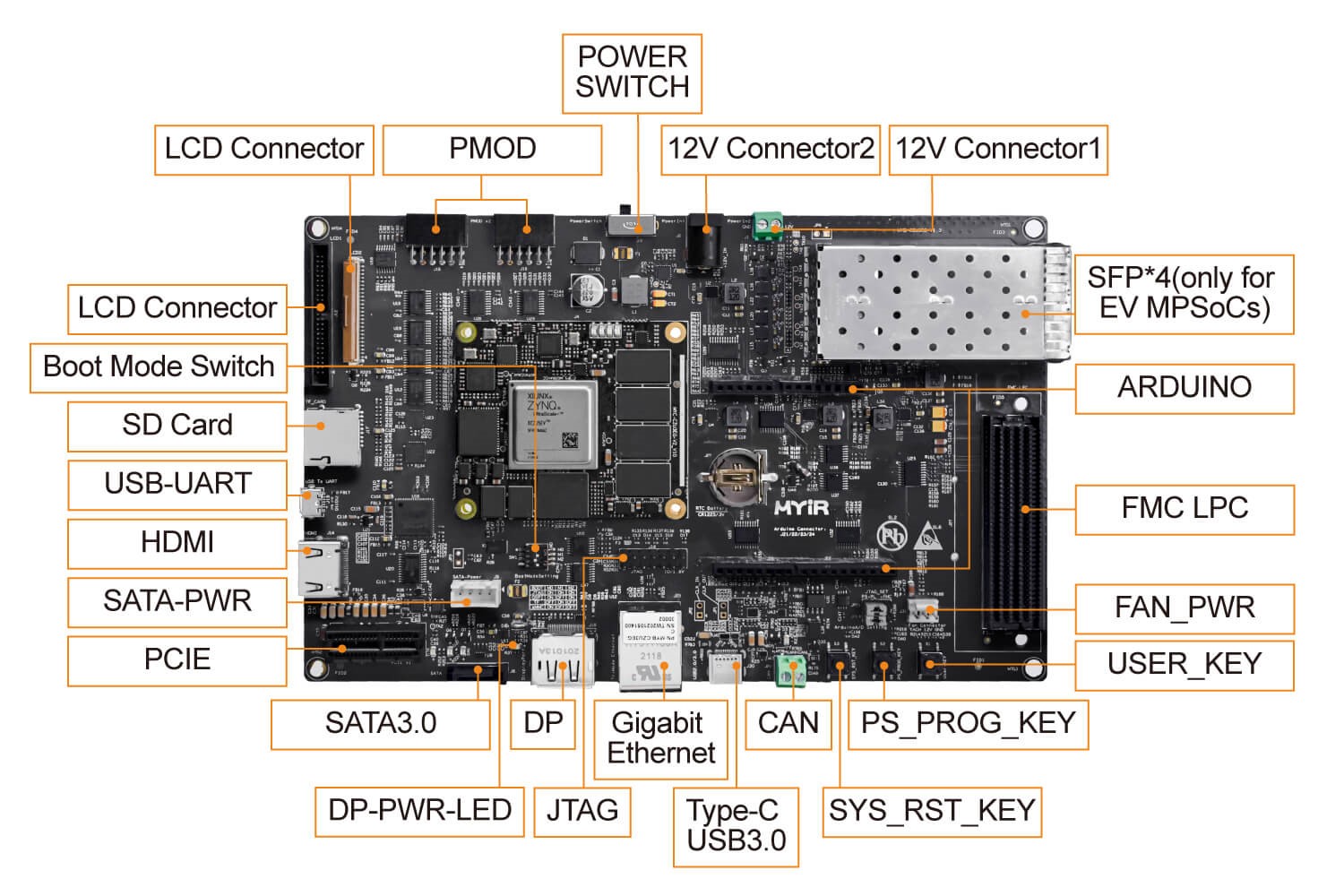

米爾的 ZU3EG 開發(fā)板憑借其可重構(gòu)架構(gòu)為 AI 和計(jì)算密集型任務(wù)提供了支持,同時(shí)避免了 7nm 工藝對(duì)國(guó)產(chǎn)芯片設(shè)計(jì)的制約。通過在 ZU3EG 上部署 Tiny YOLO v4,我們可以為智能家居、智慧城市等 AIoT 應(yīng)用提供高效的解決方案。

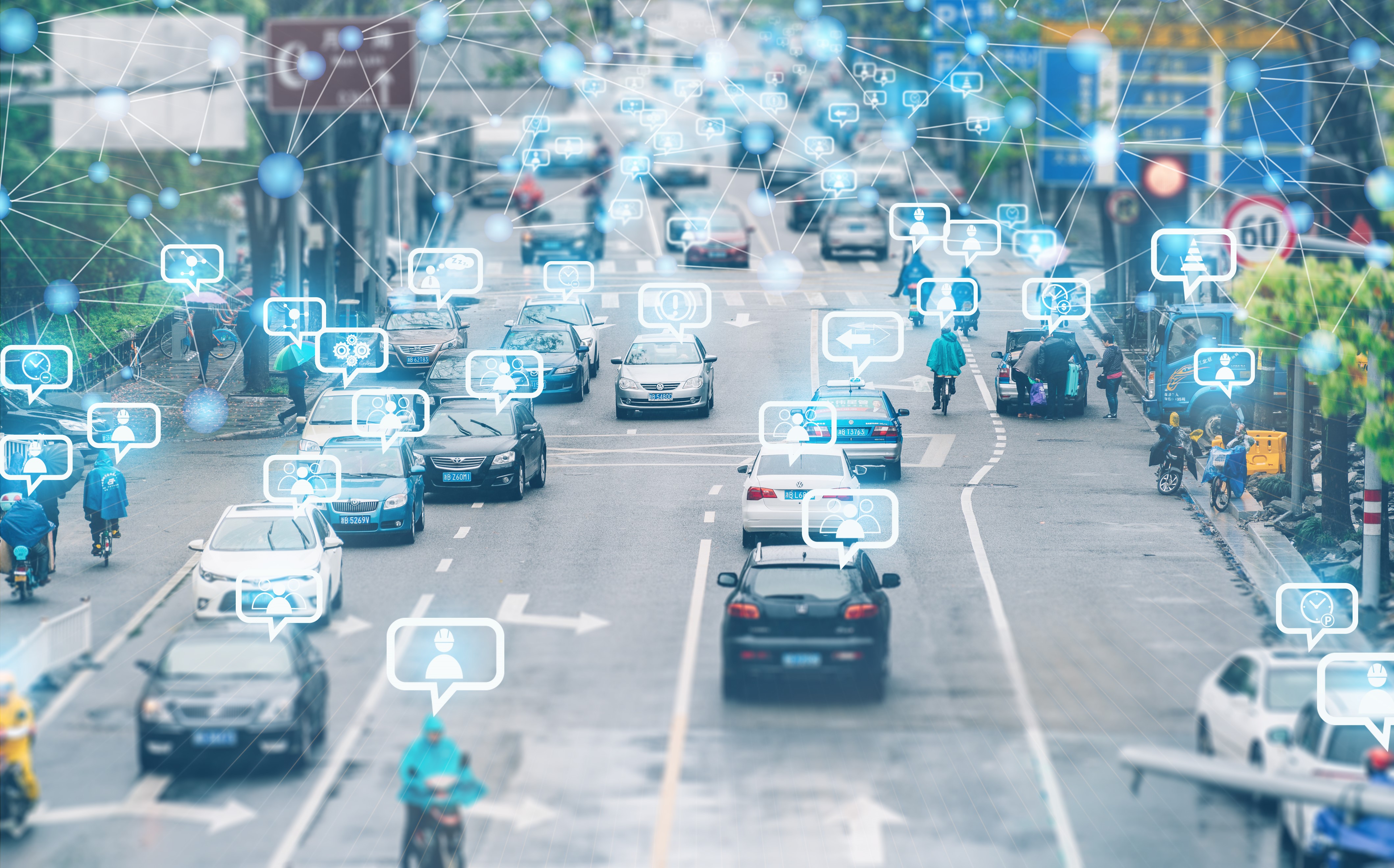

CPU GPU FPGA 架構(gòu)對(duì)比

二、 了解 Tiny YOLO 模型及其適用性

YOLO(You Only Look Once)是一種實(shí)時(shí)物體檢測(cè)模型,它通過一次性掃描整個(gè)圖像,實(shí)現(xiàn)高效的對(duì)象識(shí)別。

而其簡(jiǎn)化版 Tiny YOLO v4 更適合嵌入式設(shè)備,具有較少的層數(shù)和參數(shù)。其輕量化特性更適合在資源受限的設(shè)備上運(yùn)行,尤其在低功耗、實(shí)時(shí)檢測(cè)的邊緣計(jì)算設(shè)備中表現(xiàn)出色。

相比傳統(tǒng) GPU,F(xiàn)PGA 能在小面積和低功耗下實(shí)現(xiàn)類似的推理性能,非常契合 AIoT 應(yīng)用。像米爾 ZU3EG 這樣的 FPGA 開發(fā)板,通過底板和豐富接口的載板設(shè)計(jì),非常適合高效的嵌入式低功耗數(shù)據(jù)處理。

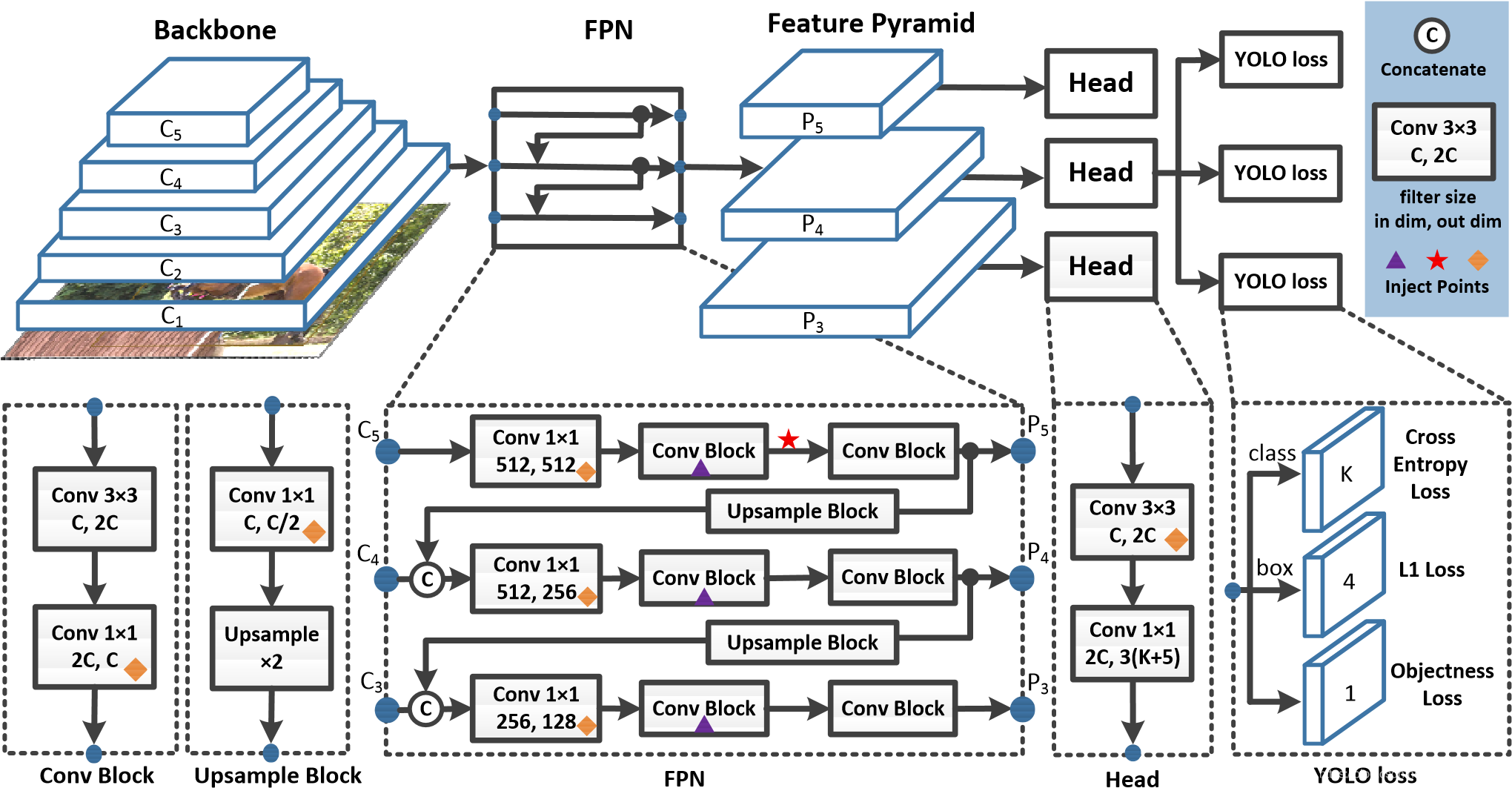

Yolo V4 網(wǎng)絡(luò)結(jié)構(gòu)圖

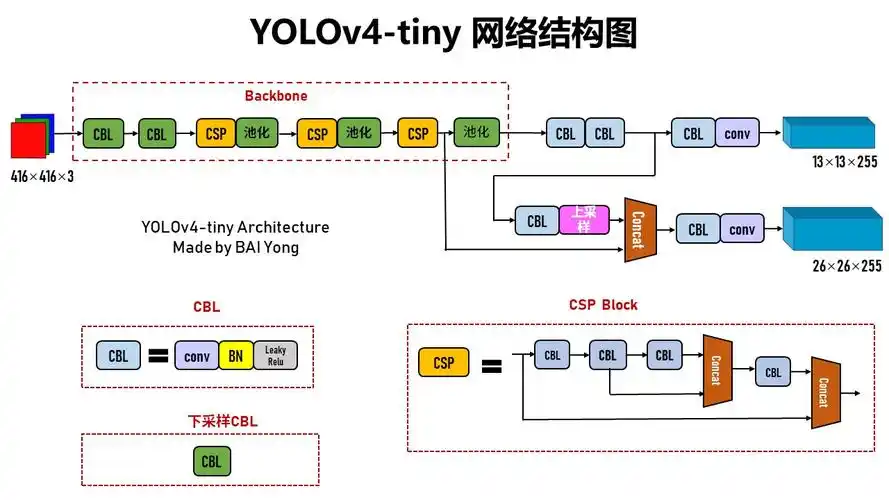

Tiny Yolo V4 網(wǎng)絡(luò)結(jié)構(gòu)圖

(通過優(yōu)化網(wǎng)絡(luò)結(jié)構(gòu)和參數(shù),保持較高檢測(cè)精度的同時(shí),降低模型的計(jì)算量和內(nèi)存占用)

三、 獲取數(shù)據(jù)集和模型

可下載開源訓(xùn)練集或預(yù)訓(xùn)練模型。為了確保兼容性,建議將模型轉(zhuǎn)換為 ONNX 格式,以便后續(xù)能在 FPGA 上完成優(yōu)化。

1. 下載 Tiny YOLO v4 模型:從 Darknet 的 GitHub 倉庫 獲取 Tiny YOLO 的預(yù)訓(xùn)練權(quán)重,或者在 COCO 等數(shù)據(jù)集上自行訓(xùn)練模型。自定義的模型適用于特定應(yīng)用場(chǎng)景(如車輛檢測(cè)、人臉檢測(cè)等)。

2. 數(shù)據(jù)準(zhǔn)備:若要自定義模型,可使用 LabelImg 等工具對(duì)數(shù)據(jù)集進(jìn)行標(biāo)注,將數(shù)據(jù)轉(zhuǎn)為 YOLO 格式。之后,可將 YOLO 格式轉(zhuǎn)換為 ONNX 格式,以便兼容 FPGA 優(yōu)化工具鏈。

Tiny YOLO 在 Darknet 上訓(xùn)練的截圖

四、 通過 Vivado HLS 為 FPGA 準(zhǔn)備模型

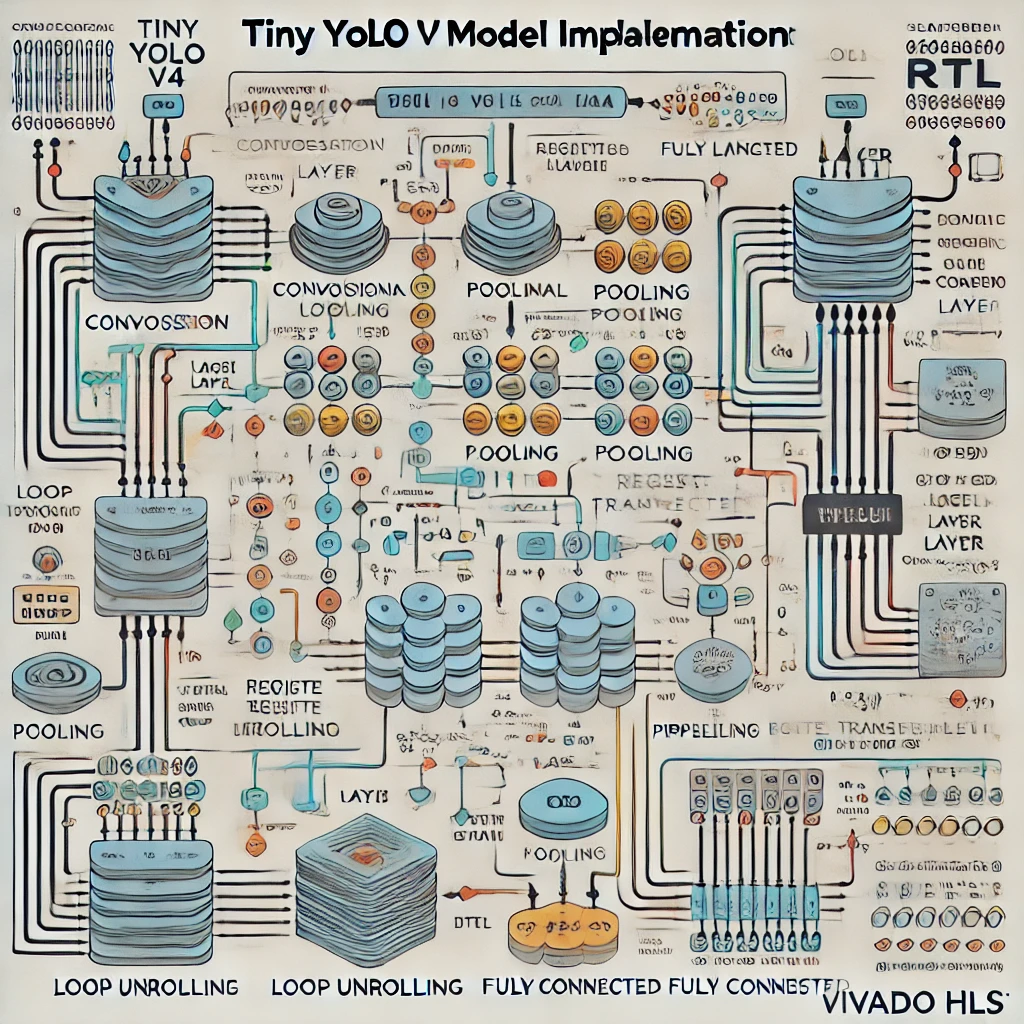

要將模型部署到 FPGA,需要將神經(jīng)網(wǎng)絡(luò)操作轉(zhuǎn)換為硬件級(jí)描述。使用 Xilinx 的 Vitis HLS(高級(jí)綜合)可以將 Tiny YOLO v4 的 C++ 模型代碼的轉(zhuǎn)化為 Verilog RTL(寄存器傳輸級(jí))代碼,從而將模型從軟件世界帶入硬件實(shí)現(xiàn)。

詳細(xì)步驟:

1. 模型層映射和優(yōu)化:

• 將 YOLO 的每一層(如卷積層、池化層)映射為硬件友好的 C/C++ 結(jié)構(gòu)。例如,將卷積映射為乘累加(MAC)數(shù)組,通過流水線實(shí)現(xiàn)并行化。

2. 算子加速與指令優(yōu)化:

• 流水線(Pipelining):利用流水線來處理多項(xiàng)操作并行,減少延遲。

• 循環(huán)展開(Loop Unrolling):展開循環(huán),以每周期處理更多數(shù)據(jù),尤其在卷積操作中有效。

• 設(shè)置 DATAFLOW 指令,使層間獨(dú)立處理。

3. 量化與位寬調(diào)整:

• 將激活值和權(quán)重量化為定點(diǎn)精度(例如 INT8),而非浮點(diǎn)數(shù)。這在維持準(zhǔn)確度的同時(shí)顯著降低計(jì)算量,尤其適合 FPGA 的固定點(diǎn)運(yùn)算支持。

Tiny YOLO 模型在 Vivado HLS 中的層層轉(zhuǎn)化流程圖

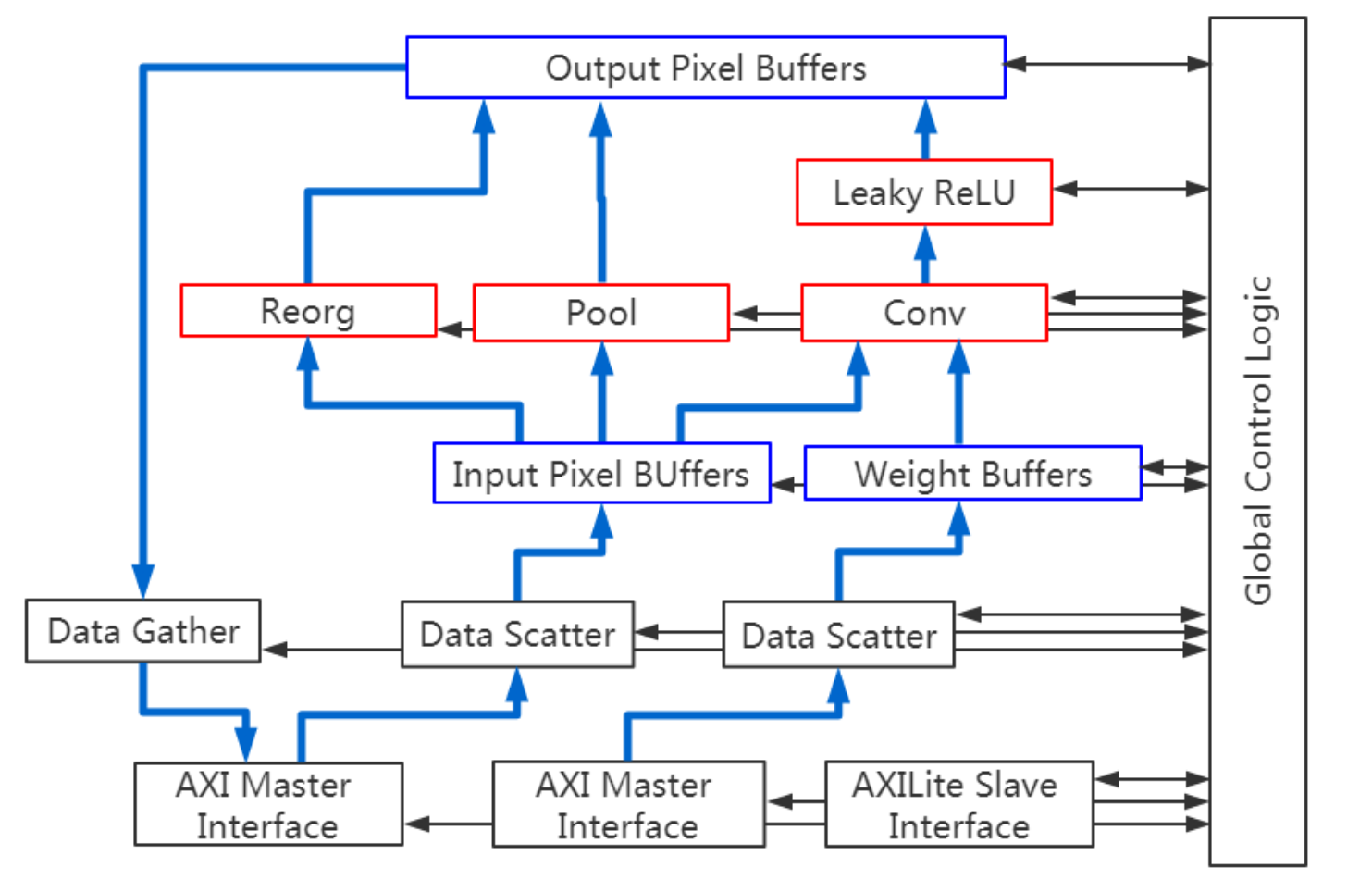

五、 使用 Vivado 綜合與部署 Verilog 到 米爾的ZU3EG FPGA開發(fā)板

當(dāng) HLS 生成的 RTL 代碼準(zhǔn)備就緒后,可以使用 Vivado 將模型部署到 FPGA。

1. Vivado 中的設(shè)置:

• 將 HLS 輸出的 RTL 文件導(dǎo)入 Vivado。

• 在 Vivado 中創(chuàng)建模塊設(shè)計(jì),包括連接AXI 接口與 ZU3EG 的 ARM 核連接。

2. I/O 約束與時(shí)序:

• 定義 FPGA 的 I/O 引腳約束,以匹配 ZU3EG 板的特定管腳配置。配置時(shí)鐘約束以滿足合適的數(shù)據(jù)速率(如視頻數(shù)據(jù) 100-200 MHz)。

• 進(jìn)行時(shí)序分析,確保延遲和響應(yīng)速度達(dá)到實(shí)時(shí)要求。

3. 生成比特流并下載到 ZU3EG:

• 生成的比特流可以直接通過 JTAG 或以太網(wǎng)接口下載到 ZU3EG。

將 Tiny YOLO 處理模塊連接到 米爾ZU3EG開發(fā)板 的外設(shè)和接口

將 Tiny YOLO 處理模塊連接到 米爾ZU3EG開發(fā)板 的外設(shè)和接口

六、 在 FPGA 上測(cè)試并運(yùn)行推理

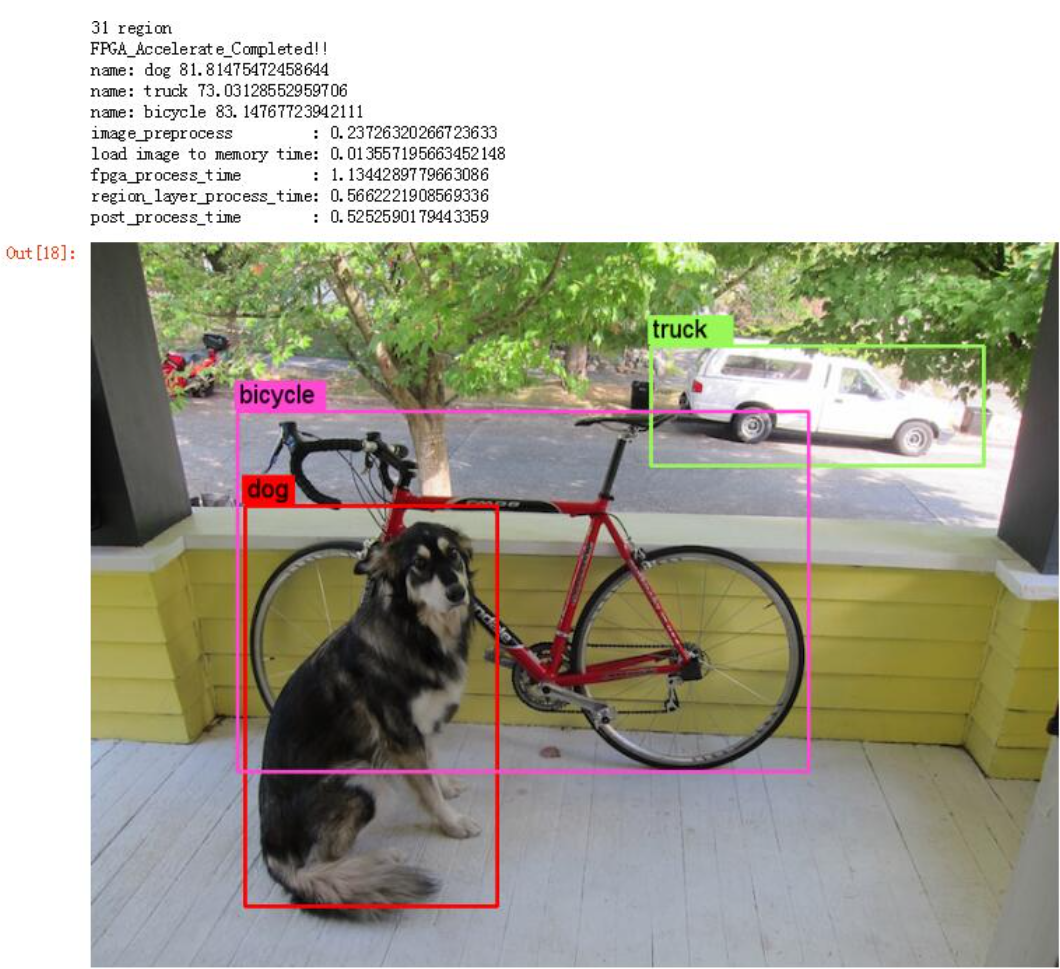

現(xiàn)在 Tiny YOLO 已部署,可以驗(yàn)證其實(shí)時(shí)對(duì)象檢測(cè)性能。

1. 數(shù)據(jù)采集:

• 通過連接的相機(jī)模塊捕捉圖像或視頻幀,或者使用存儲(chǔ)的測(cè)試視頻。

• 使用 ZU3EG 的 ARM 核上的 OpenCV 對(duì)幀進(jìn)行預(yù)處理,再將它們傳入 FPGA 預(yù)處理后進(jìn)行推理。

2. 后處理與顯示:

• 模型檢測(cè)對(duì)象后,輸出邊框和類別標(biāo)簽。使用 OpenCV 將邊框映射回原始幀,并在每個(gè)檢測(cè)到的對(duì)象周圍顯示類別和置信度。

3. 性能測(cè)試:

• 測(cè)量幀速率(FPS)和檢測(cè)準(zhǔn)確度。微調(diào)量化位寬或數(shù)據(jù)流參數(shù),以優(yōu)化實(shí)時(shí)需求。

Tiny YOLO 模型在 ZU3EG 上顯示檢測(cè)結(jié)果的實(shí)時(shí)輸出,視頻幀中標(biāo)注了檢測(cè)到的對(duì)象

Tiny YOLO 模型在 ZU3EG 上顯示檢測(cè)結(jié)果的實(shí)時(shí)輸出,視頻幀中標(biāo)注了檢測(cè)到的對(duì)象

七、 性能優(yōu)化與調(diào)試技巧

為提高性能,可以進(jìn)行以下調(diào)整:

• 內(nèi)存訪問:設(shè)計(jì)數(shù)據(jù)存儲(chǔ)方式,最大限度利用緩存并減少數(shù)據(jù)傳輸,降低內(nèi)存瓶頸。

• 降低延遲:重新評(píng)估關(guān)鍵路徑延遲。若延遲過高,調(diào)整 Vitis HLS 中的流水線深度,并驗(yàn)證層間的數(shù)據(jù)依賴性。

• 量化改進(jìn):嘗試 INT8 量化。Xilinx 的 Vitis AI 可幫助微調(diào)量化參數(shù),以平衡準(zhǔn)確性與速度。

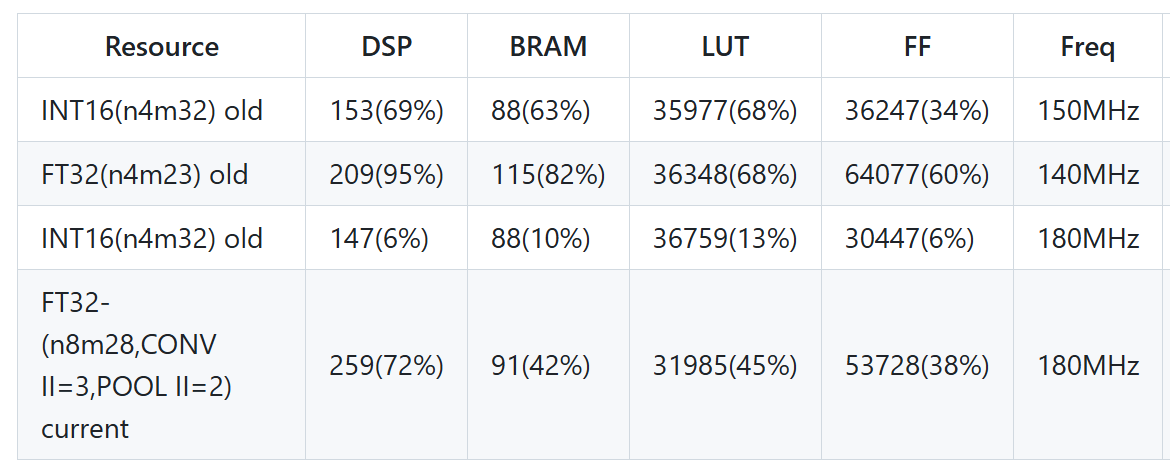

不同優(yōu)化配置對(duì)資源使用的影響

圖:米爾MYC-CZU3EG/4EV/5EV-V2核心板及開發(fā)板

在MYIR 的 ZU3EG 開發(fā)平臺(tái)上提供了一種高效的解決方案。利用 FPGA 獨(dú)特的靈活性和低功耗優(yōu)勢(shì),助力未來 AIoT 設(shè)備的普及和智能升級(jí)。

關(guān)注米爾電子公眾號(hào),后臺(tái)回復(fù)FPGA,獲取完整Tiny Yolo V4教程。

相關(guān)新聞

- ? 米爾出席2025安路科技FPGA技術(shù)沙龍

- ? 新品!米爾NXP i.MX 91核心板開發(fā)板,賦能新一代入門級(jí)Linux應(yīng)用

- ? 米爾RK3576核心板適配多種系統(tǒng),解鎖多樣化應(yīng)用

- ? 3核A7+單核M0多核異構(gòu),米爾全新低功耗RK3506核心板發(fā)布

- ? 喜訊!米爾電子與安路科技達(dá)成IDH生態(tài)戰(zhàn)略合作,共筑FPGA創(chuàng)新生態(tài)

- ? 免費(fèi)送30套開發(fā)板!米爾-安路飛龍派創(chuàng)意秀限時(shí)活動(dòng)

- ? 一篇文章帶您玩轉(zhuǎn)T113的ARM+RISC-V+DSP三核異構(gòu)!

- ? 瑞薩交流日進(jìn)行中,米爾演講-RZ/T2H高性能模組賦能工業(yè)產(chǎn)品創(chuàng)新

- ? 米爾閃耀德國(guó)紐倫堡Embedded World 2025,展現(xiàn)嵌入式技術(shù)無限可能

- ? 4核CPU,ARM中量級(jí)多面手,米爾瑞芯微RK3562核心板上市

編輯精選

- ? PLC市場(chǎng)穩(wěn)定回暖,國(guó)產(chǎn)化進(jìn)程加速推進(jìn)

- ? 鴻道操作系統(tǒng)在京首發(fā) 突破“大小腦”核心技術(shù)開啟自主可控具身智能新紀(jì)元

- ? 2025年施耐德電氣創(chuàng)新峰會(huì)盛大開幕

- ? ABB 加速器中國(guó)周為創(chuàng)新加速

- ? 羅克韋爾自動(dòng)化發(fā)布第十版《智能制造現(xiàn)狀報(bào)告》

- ? 西門子舉辦“Realize LIVE”大會(huì)

- ? 埃夫特牽頭成立 “高速高精技術(shù)創(chuàng)新聯(lián)合體”,助力長(zhǎng)三角一體化發(fā)展

- ? 匯川技術(shù)分拆聯(lián)合動(dòng)力上市,關(guān)聯(lián)交易增收引關(guān)注

- ? 東土科技參與國(guó)家重點(diǎn)研發(fā)計(jì)劃 ,共同研發(fā)工業(yè)智控創(chuàng)新技術(shù)

- ? 2025華南國(guó)際工業(yè)博覽會(huì)圓滿閉幕

工控原創(chuàng)

- ? 一文get六月工控自動(dòng)化大事

- ? ABB加速器中國(guó)周:當(dāng)AI邂逅硬核工業(yè),一場(chǎng)自下而上的智造革命

- ? 點(diǎn)擊了解5月工控圈那些事兒

- ? 分拆上市還是出售?ABB機(jī)器人業(yè)務(wù)將何去何從

- ? 打造標(biāo)桿案例及生態(tài)圈,ABB全力推動(dòng)Ethernet-APL應(yīng)用加速

- ? 你關(guān)心的四月份工控大事全在這里

- ? 匯川技術(shù)2024年財(cái)報(bào)解析:多元化布局彰顯增長(zhǎng)韌性

- ? 關(guān)稅政策讓美國(guó)工業(yè)自動(dòng)化復(fù)蘇之路面臨不確定性

- ? ADI系統(tǒng)級(jí)創(chuàng)新方案深度賦能工業(yè)智能化與能源安全

- ? 32篇新聞,帶你回顧3月工控圈熱點(diǎn)